# Chapitre I

## CIRCUITS INTÉGRÉS À APPLICATIONS SPÉCIFIQUES (ASICS) ANALOGIQUES

### 1 - LA PLACE DES ASICS EN ÉLECTRONIQUE

#### 1.1 Définitions des ASICS

Un Circuit Intégré à Applications Spécifiques ou ASIC ("Application Specific Integrated Circuit" en Anglais) est un circuit intégré qui a été conçu exclusivement pour une application particulière bien déterminée. Les développements les plus rapides et les plus importants ont eu lieu dans le domaine de l'électronique numérique. La technologie essentiellement utilisée y est le CMOS. Le domaine de l'électronique digitale se prête assez facilement à cette approche compte tenu de la répétitivité des cellules utilisées (portes).

En analogique, compte tenu de la relative complexité et de la différence des fonctions utilisées les développements ont été plus lents. Les technologies utilisées sont le Bipolaire et le CMOS. Des réseaux mixtes, souvent en technologie BiCMOS, comportant sur un même substrat une partie réservée aux fonctions analogiques, l'autre aux fonctions numériques sont aussi disponibles sur le marché.

#### 1.2 Avantages, inconvénients liés aux circuits ASICS

L'utilisation de circuits ASICS a rendu possible l'intégration de plusieurs fonctions sur une même "puce". Ces circuits permettent ainsi :

- un gain de performances (longueurs des connexions plus réduites),

- un gain de place (un seul circuit pour remplacer plusieurs fonctions),

- une meilleure fiabilité (moins de connexions et circuit plus compact),

- d'assurer la confidentialité (fonction réalisée pratiquement incopiable).

Cependant la réalisation de ces circuits nécessite :

- des investissements importants (postes de CAO électronique et logiciels correspondants)

- un personnel hautement qualifié (concepteurs).

Les circuits ASIC ont permis l'émergence de sociétés indépendantes qui se sont spécialisées dans la "conception", et travaillent parallèlement aux grands "groupes traditionnels".

### 2 - LES RÉSEAUX BIPOLAIRES ANALOGIQUES

Les réseaux bipolaires analogiques actuels se répartissent en trois grandes familles :

- les réseaux prédiffusés qui comportent uniquement des composants (transistors, R, C, ...)

- les réseaux précaractérisés, comprenant à la fois des fonctions analogiques (par exemple : amplificateurs opérationnels, comparateurs...) et des composants.

- les réseaux mixtes, comprenant des fonctions logiques (portes, ...) et des composants.

Les réseaux prédiffusés, dont certains comprennent des transistors PNP verticaux, sont ceux qui seront les mieux adaptés à la réalisation de fonctions analogiques rapides, nous les étudierons donc plus en détail.

La réalisation du circuit ASIC est donc obtenue par configuration d'un réseau de départ sous forme standard afin de réaliser l'application souhaitée. Cette configuration qui nécessite la réalisation de connexions entre composants ou macrofonctions, est obtenue à partir d'une ou de plusieurs opérations de métallisation. Les circuits ainsi obtenus à partir de réseaux standards font partie des circuits "semi-customs" (ou partiellement à la demande). Il faut remarquer qu'un nombre plus ou moins important de composants du réseau ne seront pas utilisés dans l'application envisagée.

Un circuit "full- custom" (ou totalement à la demande) permet de n'intégrer sur le Silicium, que les composants réellement nécessaires à l'application prévue. Il est alors possible, avec l'habitude, de s'arranger pour que chaque composant occupe sur la "puce" une place conduisant aux meilleures performances.

Cependant la topologie optimale pour laquelle chaque composant occuperait la place idéale devrait être déterminée automatiquement à partir des paramètres dynamiques de la fonction (Bande passante... etc) que l'on souhaite réaliser.

De telles possibilités qui n'existent pas encore dans le domaine des circuits analogiques, devraient faire cependant appel à des fonctions logicielles qui sont généralement désignées sous le nom de "compilateurs de Silicium".

## 2.1 Les réseaux mixtes

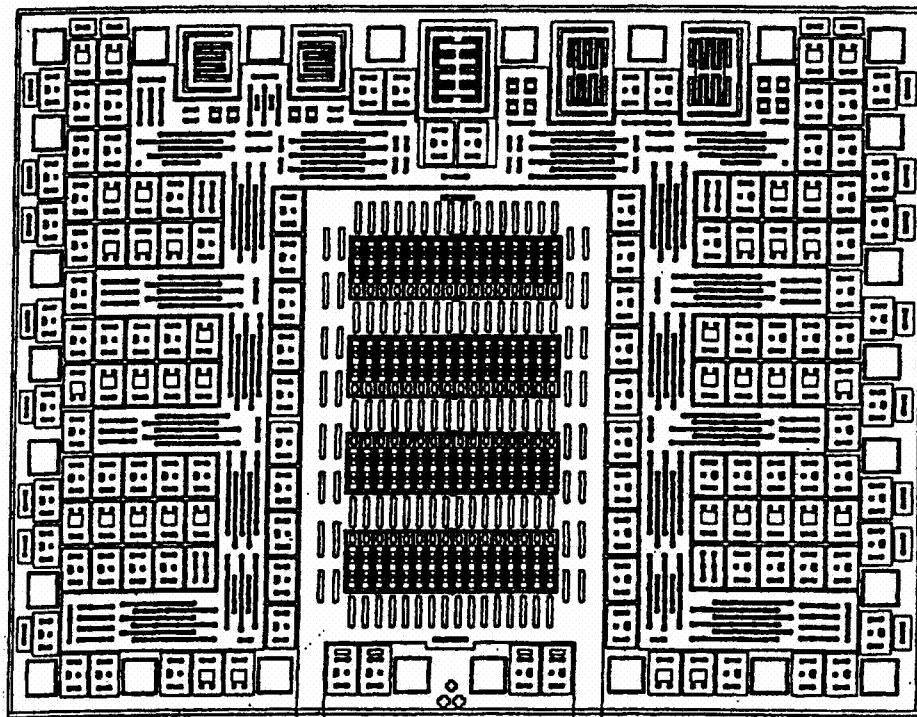

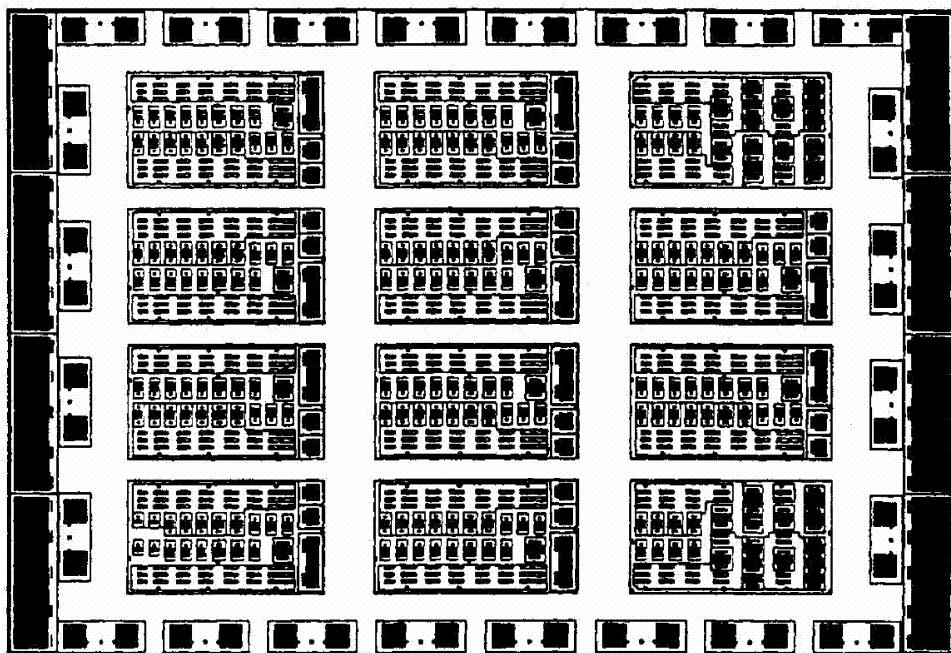

*Fig. 1 : Réseau bipolaire mixte Génésis 1100 .*

Copyright Semiconductor Components Industries, LLC, précédemment

Cherry Semiconductor. Reproduit avec autorisation.

Le réseau Genesis 1100 (Cherry Semiconductor) représenté sur la figure 1, est l'exemple type d'un réseau mixte. Il comprend une partie de la puce (au centre) réservée aux fonctions logiques qui seront obtenues par connexion de portes logiques de type I<sup>2</sup>L (*Integrated Injection Logic*). Il contient 64 portes logiques dont les temps de propagation sont ajustables entre 50 ns et 7 µs, des cellules Schottky d'interface et des transistors de puissance qui peuvent fournir des courants de 400 mA.

Des transistors PNP (41) et NPN (102) ainsi que des résistances (347) sont présents autour. Les plots d'entrée-sortie (26) sont disposés à la périphérie.

## 2.2 Les réseaux précaractérisés

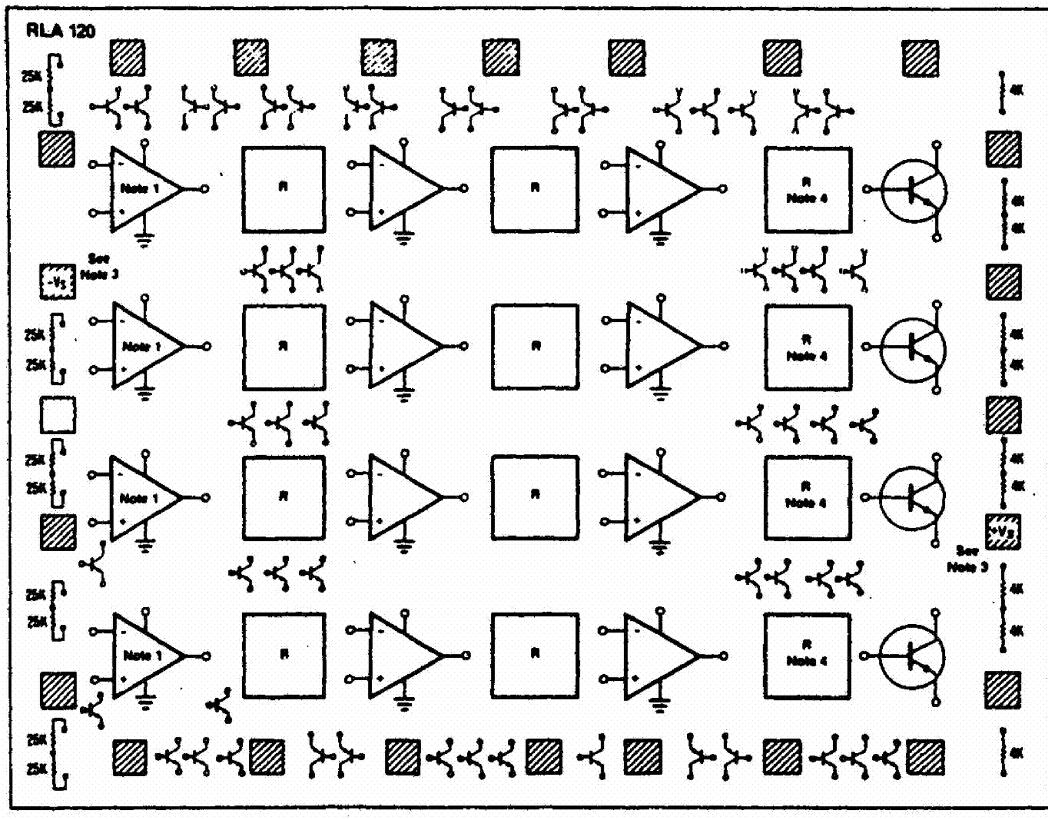

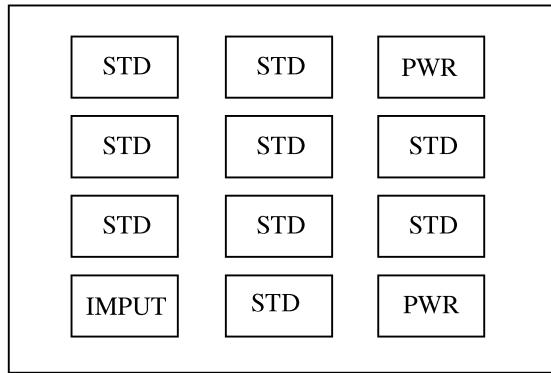

Le réseau RLA 120 (Raytheon Compagny) dont la représentation symbolique est donnée *figure 2* en est l'exemple type. Il comprend 12 macro cellules qui peuvent être configurées, à l'aide de différentes connexions, sous forme d'amplificateurs opérationnels standards type 741, ou sous forme de comparateurs de tension type LM139.

Des réseaux de résistances de forte valeur y sont aussi présents. Des transistors PNP et NPN standards et 4 transistors NPN à fort courant de collecteur ( $\approx 200$  mA), type 2N2222 sont aussi disponibles.

Le schéma simplifié de la *figure 2* indique l'emplacement des différentes fonctions.

*Fig. 2 : Réseau bipolaire précaractérisé RLA 120.*

Copyright Raytheon.

Les caractéristiques des fonctions réalisables à partir des différentes macro-cellules sont données par le constructeur pour différentes conditions de test, d'où le nom de réseaux précaractérisés.

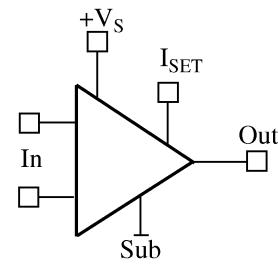

La *figure 3* indique à titre d'exemple les caractéristiques d'un des amplificateurs opérationnel de ce réseau. Cet amplificateur, noté MOPA1, est réalisé à partir de trois autres macro-cellules élémentaires (MGS, MPND et MND). Il peut être utilisé avec une alimentation simple ( $0, + 15$  V) ou double ( $\pm 15$  V).  $I_{SET}$  est le courant de polarisation de l'amplificateur opérationnel.

Macrocell Op Amp MOPA1, DC Electrical Characteristics.

$(V_S = \pm 15V, I_{SETX} = 10 \mu A, \text{ and } T_A = + 25^\circ C$

unless otherwise specified)

| Parameters                                                                           | Test Conditions                         | LCL      | Typ        | UCL       | Units   |

|--------------------------------------------------------------------------------------|-----------------------------------------|----------|------------|-----------|---------|

| Input Offset Voltage                                                                 | $V_{CM} = 0V$                           |          | + 1.0      | $\pm 5.0$ | mV      |

| Input Offset Current                                                                 | $V_{CM} = 0V$                           |          | 4.0        | 20        | nA      |

| Input Bias Current                                                                   | $V_{CM} = 0V$                           |          | 25         | 100       | nA      |

| Large Signal Voltage Gain                                                            | $R_L \geq 10k\Omega, V_{OUT} = \pm 10V$ | 74       | 85         |           | dB      |

| Input Voltage Range                                                                  |                                         | $\pm 13$ | $\pm 14.5$ |           | V       |

| Common Mode Rejection Ratio                                                          | $R_S \leq 10 k \Omega$                  | 70       | 95         |           | dB      |

| Power Supply Rejection Ratio                                                         | $R_S \leq 10 k \Omega$                  | 70       | 95         |           | dB      |

| Output Voltage Swing                                                                 | $R_L \geq 10 k\Omega$                   | $\pm 10$ | $\pm 14$   |           | V       |

| Supply Current (Each Cell)                                                           | $R_L = \infty$                          |          | 80         | 160       | $\mu A$ |

| Short Circuit Current                                                                |                                         |          | $\pm 5$    |           | mA      |

| $V_S = \pm 15V, I_{SETX} = 1\mu A, T_A = + 25^\circ C$ unless otherwise specified    |                                         |          |            |           |         |

| Large Signal Voltage Gain                                                            | $R_L = \infty, V_{OUT} = \pm 10 V$      |          | 80         |           | dB      |

| Input Offset Voltage                                                                 | $V_{CM} = 0V$                           |          | + 0.5      | $\pm 5.0$ | mV      |

| Input Bias Current                                                                   | $V_{CM} = 0V$                           |          | 2.0        | 10        | nA      |

| Supply Current (Each Cell)                                                           | $R_L = \infty$                          |          | 8          | 20        | $\mu A$ |

| $V_S = \pm 1.5V, I_{SETX} = 10 \mu A, T_A = + 25^\circ C$ unless otherwise specified |                                         |          |            |           |         |

| Input Offset Voltage                                                                 | $V_{CM} = 0V$                           |          | +0.5       | $\pm 5.0$ | mV      |

| Input Voltage Range                                                                  |                                         |          | $\pm 0.7$  |           | V       |

| Common Mode Rejection Ratio                                                          |                                         |          | 80         |           | dB      |

| Output Voltage Swing                                                                 | $R_L \geq 10 k\Omega$                   |          | $\pm 0.6$  |           | V       |

**Fig. 3 : Caractéristiques de l'amplificateur opérationnel MOPA1

(Réseau Raytheon RLA 120).**

Copyright Raytheon.

## 2.3 Les réseaux prédiffusés

### a) Exemples de réseaux prédiffusés bipolaires

Les réseaux prédiffusés bipolaires analogiques comportent un nombre plus ou moins important de composants : transistors PNP (verticaux, latéraux ou "substrat"), transistors NPN, résistances, capacités à valeur programmable, capacités fixes.

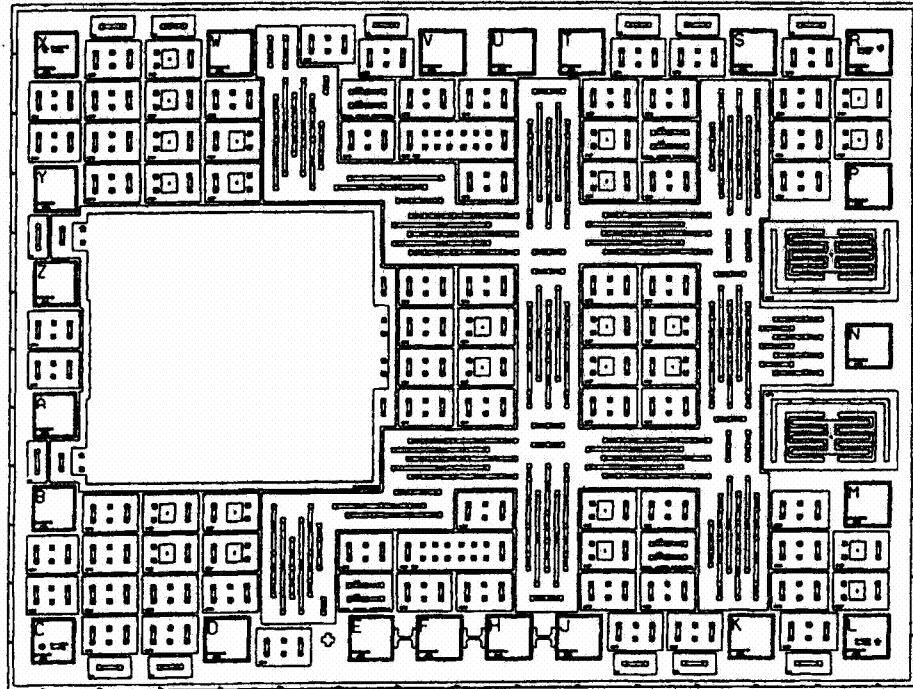

Le réseau bipolaire Génésis 3500 (Cherry Semiconductor), reproduit sur la figure 4, a la particularité de posséder un photo détecteur.

Il comprend en outre 59 transistors NPN, 24 transistors PNP, 2 transistors NPN de puissance et 214 résistances.

**Fig. 4 : Réseau linéaire Genesis 3500 (Cherry Semiconductor).**

Copyright Semiconductor Components Industries, LLC, précédemment

Cherry Semiconductor. Reproduit avec autorisation.

Dans un réseau prédiffusé les composants sont généralement regroupés dans des blocs ("tiles" en Anglais) dont certains (les modules standards) sont reproduits plusieurs fois sur le substrat. La *figure 5* représente la disposition adoptée pour les réseaux bipolaires de type ALA 202 de chez ATT. La localisation des différents blocs y apparaît très clairement en *5 b*).

**5 a ) : Module Layout**

**5 b ) : Location of Tiles on Chip**

**Fig. 5 : Réseau ALA 202 (ATT) et localisation des différents blocs.**

Copyright AT&T.

Le réseau comprend 8 blocs standard identiques notés STD, 1 bloc d'entrée noté INPUT et 2 blocs de puissance (PWR) réservés aux circuits de sortie. Les blocs diffèrent par le type de transistor qu'ils contiennent. Un bloc standard, comporte des transistors PNP et NPN dont les surfaces d'émetteur sont 1X, 2X ou 5X prévus pour des courants de collecteur respectivement inférieurs à 4, 8 ou 20 mA. Un bloc d'entrée comportera de même des transistors 1/3X 1X et 2X pour des courants de 1, 2 ou 8 mA, alors que pour un bloc de puissance les surfaces sont 1X, 2X, 5X et 15X et les courants correspondants 4, 8, 20 et 60 mA.

### b) Transistors Intégrés dans les réseaux

- **Transistors NPN**

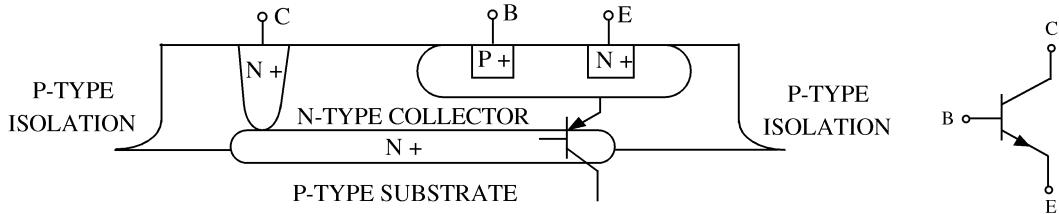

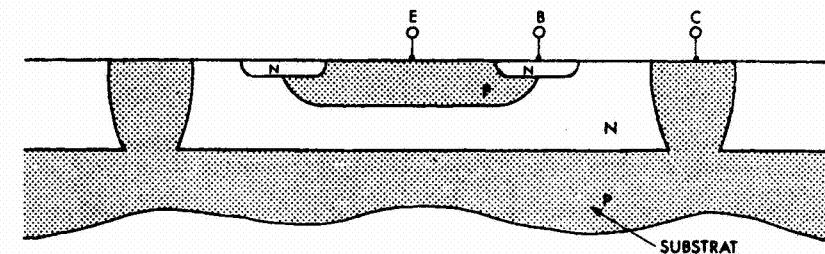

Les caractéristiques des transistors NPN des réseaux bipolaires analogiques sont similaires à celles des transistors discrets réalisés en technologies planar. La représentation du transistor NPN intégré est donnée *figure 6*. Deux effets parasites peuvent être mis en évidence.

**Fig. 6 : Transistor NPN intégré.** Copyright AT&T.

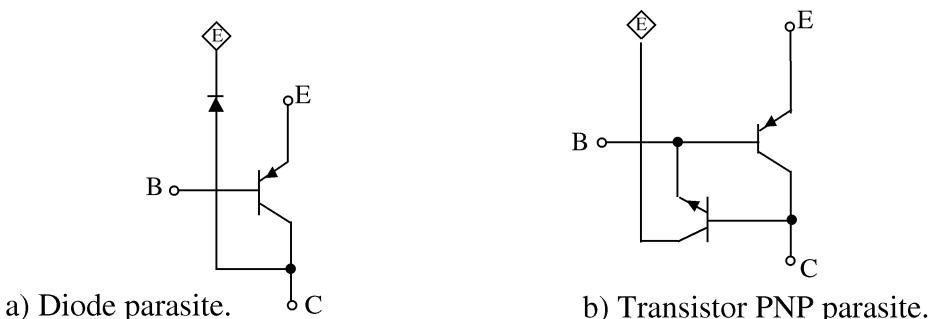

Lorsque le transistor NPN est polarisé en direct, une diode polarisée en inverse interviendra par sa capacité parasite qui apparaît entre collecteur et substrat. (*figure 7 a*).

Si le transistor NPN atteint la zone de saturation, la jonction collecteur-base du transistor parasite PNP équivalent devient conductrice (*figure 7 b*).

**Fig. 7: Éléments parasites du transistor NPN.**

Leurs gain en courant  $\beta$  dépassent généralement la centaine, et leurs fréquences de transition qui dépendent de la technologie utilisée, sont actuellement souvent supérieures à 10 GHz.

- **Transistors PNP**

Différents types de transistors PNP dont les performances sont très différentes peuvent être présents sur les réseaux bipolaires.

- o *Transistors PNP substrat*

Les collecteurs des différents transistors sont ici tous connectés au substrat (*figure 8*). Les fréquences de transition de ces PNP peuvent atteindre quelques 100 MHz, mais leurs possibilités d'utilisation sont très réduites à cause des connections précédentes.

**Fig. 8 : Transistor PNP substrat.**

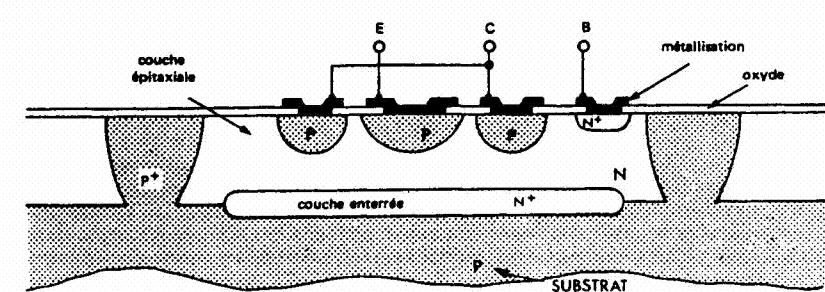

- o *Transistors PNP latéraux*

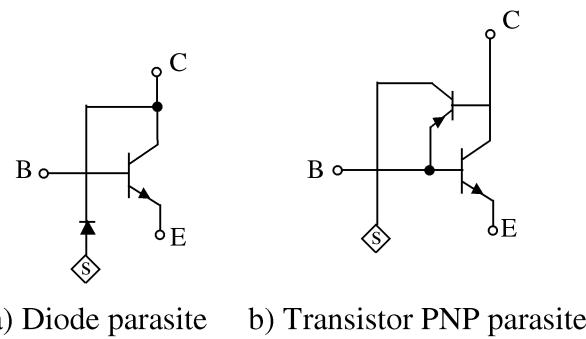

Ces transistors sont utilisés par de nombreux constructeurs (*figure. 9*). Ils peuvent en effet être réalisés en même temps que les transistors NPN sans opérations de masquage supplémentaires. Ils possèdent cependant des performances médiocres : faibles valeurs des gains en courant  $\beta$  qui dépassent rarement 30, et fréquences de transition très souvent inférieures à 10 MHz.

**Fig. 9 : Transistor PNP latéral.**

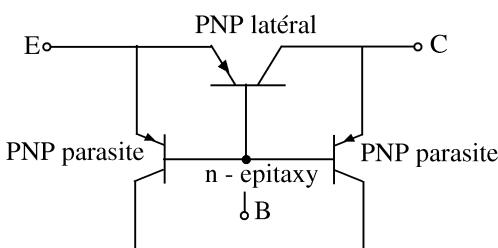

Ces limitations proviennent des transistors PNP parasites qui apparaissent d'une part entre émetteur, base et substrat et d'autre part entre collecteur, base et substrat (*figure 10*).

**Fig. 10 : Transistor PNP latéral et transistors parasites.**

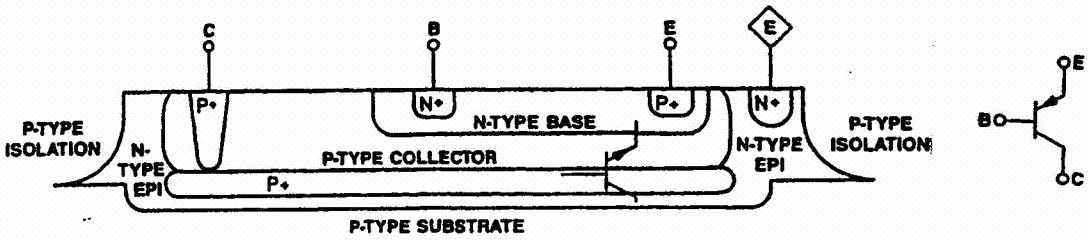

### o Transistors PNP verticaux

Bien qu'un peu moins performants que les transistors NPN verticaux, les PNP verticaux présentent d'intéressantes performances. Leurs gains en courant  $\beta$  sont généralement compris entre 40 et 100. leurs fréquences de transition qui dépendent de la technologie utilisée avoisinent ou dépassent actuellement les 10 GHz. La figure 11 représente le transistor PNP vertical intégré dans les réseaux de type ALA 200 de chez ATT.

**Fig. 11:** Transistor PNP vertical. Réseau ALA 200

Copyright AT &T.

Comme déjà vu pour le NPN, une diode polarisée en inverse qui intervient par sa capacité, apparaît entre Collecteur et Substrat (figure 12 a), lorsque le PNP est polarisé en direct. Dans la zone de saturation, c'est un transistor parasite PNP équivalent qui devient conducteur (figure 12 b).

**Fig. 12 :** Éléments parasites d'un transistor PNP vertical.

### • Appariement des caractéristiques des transistors

Les transistors sont tous intégrés en même temps sur une puce de silicium. Il en résultera donc certaines propriétés dont il sera possible de tirer partie. Ainsi, les températures des différents transistors pourront être considérées comme identiques dans la mesure où la dissipation thermique totale de la "puce" sera faible.

Les gradients de température seront en tous cas minimisés lorsque une répartition respectant une certaine symétrie aura été adoptée pour le "layout", les dimensions du réseau étant en outre toujours faibles (surface généralement inférieures à 10 mm<sup>2</sup>).

Dans des conditions de fonctionnement identiques (c'est-à-dire pour des courants de collecteurs proches), la différence existante entre les  $V_{BE}$  de deux transistors voisins d'un même type est bien souvent de l'ordre de 0,5 mV (elle dépend des transistors considérés et est par exemple dans tous les cas inférieure à 1,5 mV pour les réseaux de type ALA 200 de chez ATT). Les écarts entre les  $\beta$  des transistors de même type sont généralement de l'ordre de 1 à 5%. Ce sont ces propriétés qui ont par exemple permis le développement des circuits translinéaires (voir Chapitre III).

### c) Autres composants intégrés dans les réseaux bipolaires

Les résistances intégrées dans les réseaux peuvent être de plusieurs types :